| HOME |

| CUSTOM DESIGN |

| PRODUCTS |

| CONTACT |

| CIRCUITS |

| FAQs |

| RESOURCES |

| LINKS |

| ABOUT |

|

|

DOWNLOAD THE SIMULATOR HERE FOR NEWER EXCEL DOWNLOAD THE SIMULATOR HERE FOR OLDER VERSIONS OF EXCEL

|

||

| This is awesome. We all know excel can be

embedded with formulas to automate calculations of all kinds of data. A

cell's value can be made to depend on the values of hundred if not

thousands of neighboring or distant cells. The cell's final output need

not be the summation or product of some list of cells, it can be more

complicated. Conditional statements, like "if and then" can be embedded

into a cell to output specific values DEPENDING on a set of well

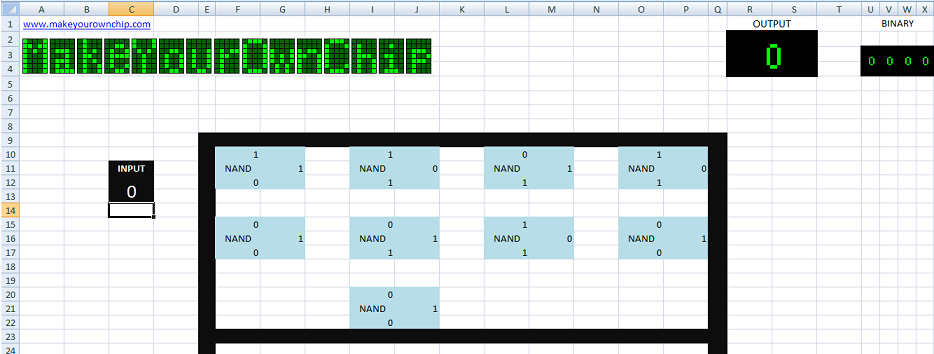

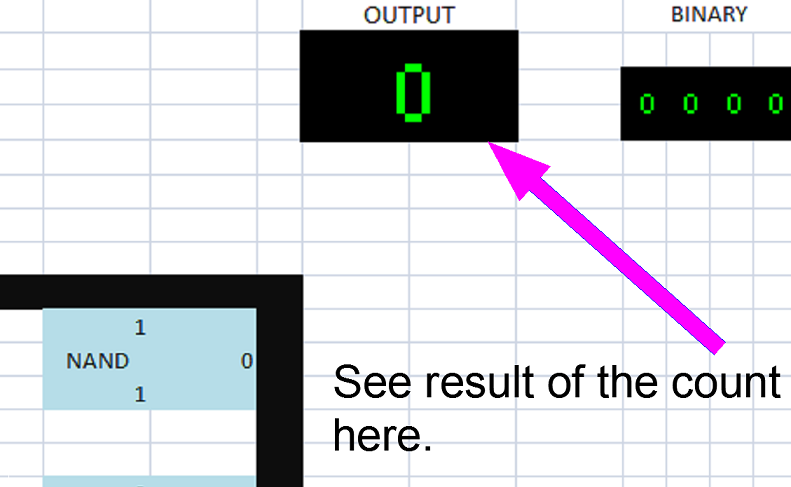

defined conditions. This if-and-then ability was exploited here, in this full function 4-bit Asynchronous T Flip Flop circuit simulator. The various NAND gates that make up this circuit, shaded in light blue, perform the super simple NAND function by executing the excel formula: if (cell1 * cell2 = 0,1,0). Meaning, if this NAND gate's two input cells, when multiplied together, equal one then output zero, otherwise, output one. It doesn't seem too interesting, but amazingly with enough NAND gates you can build yourself a whole computer. In this simulation, a total of 36 NAND gates are logically connected together inside the excel spreadsheet, as if wired together, assembling into a 4 bit cascade of T Flip Flop blocks. The function of which is to literally count the number of times the user changes the input cell from one to zero. Toggling this alternating input, 0, 1, 0, 1, 0... causes the circuit to change internally as latches open and close (represented by 0 and 1 in Excel) to capture and keep track of the count. Finally the zero ore one output of each stage is registered at the top of the spreadsheet in binary, as well as a decimal conversion showing number 0 - 15. If you look closely at the output number, you can even see the ripple effect present, which is usually too fast to notice in a transistor based design. This is the reason behind such asynchronous designs being called ripple counters. By rearranging the NAND gates a synchronous counter (with no ripple effect) can also be simulated and will be posted HERE later. |

||

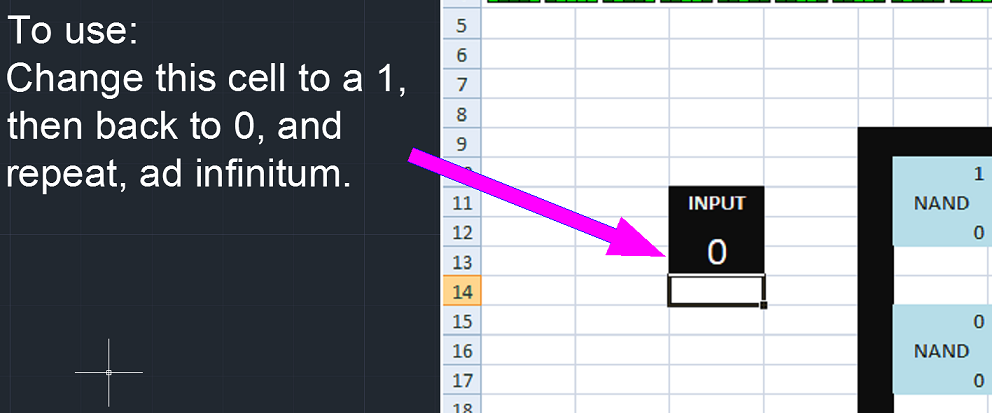

| Instructions for operation: 1. Download the spreadsheet file and open it in Excel. 2. Enable "Iterative Calculation" in Excel. This will allow for circular references which are necessary for a virtual latch circuit. This is found in option, under calculation or formulas depending on version of Excel. 3. Toggle the input cell between zero and one. Every time the cell is changed back to zero, the circuit will register a change. Keep doing it. In a slightly different model, still using Excel, I set a "conditional format" to change the cells green if they contain a "1". Here is an animation depicting the entire sequence of the 4-bit asynchronous counter. To make the animation I used 32 frames (which shows the "in between states" that are not normally seen, but internal to the flip-flops. The ripple effect, which is rapidly visible in the actual spreadsheet, was not captured here... Take a look.

The simulation works! It does not use any of Excel's Visual Basic programming of any kind, nor any scripting. Just the power of NAND gates and circular references in Excel! Interesting note: After changing the input cell's value from zero to one to zero a few times, try using the undo and redo commands (CTRL Z) and (CTRL Y). The counter will continue to count forward regardless of whether or not the user attempts to undo it. This reveals that the undo command in excess only undoes the last user input rather than reverting the document to a previous state. |

|